产业分析-3D AI晶片重塑半导体未来

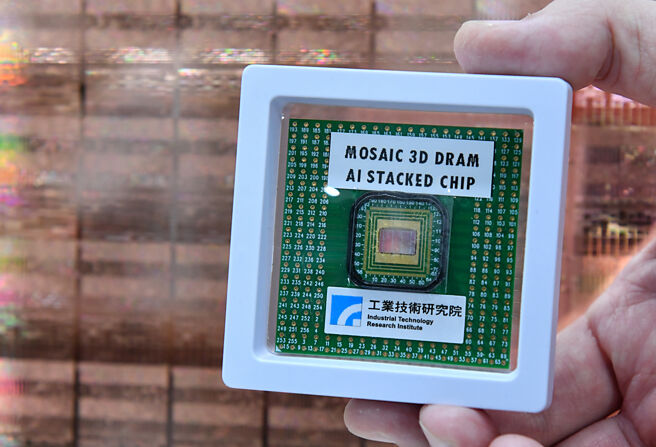

D堆叠技术能够将不同制程和不同功能的晶片整合在一起,因此它将成为异质整合技术的关键之一。图/本报资料照片

随着生成式AI(如ChatGPT)和机器学习技术的崛起,半导体企业亟需开发更高效能的AI晶片,以支持日益增长的数据处理需求。因此,如何在现有制程技术中,实现效能与成本的最佳平衡,成为业界关注重点,凸显出未来AI和晶片制造的深度融合,为全球半导体市场注入新的活力。

■3D堆叠技术的应用前景

当摩尔定律逐渐接近其物理极限,半导体产业也开始探索新的技术来提高晶片的效能。3D堆叠技术因此应运而生。这项技术通过将多层晶片垂直堆叠在一起,不仅能够提升晶片的计算能力,还能够显著减少晶片面积和功耗。

3D堆叠技术的应用潜力巨大,特别是在AI、边缘运算和高效能运算领域。这项技术使得AI晶片能够在不增加晶片面积的情况下,实现更强大的计算能力,满足自动驾驶、智慧城市、5G基站等应用对于高效能运算的需求。

同时,由于3D堆叠技术能够将不同制程和不同功能的晶片整合在一起,因此它将成为异质整合技术的关键之一,推动AI、存储器和传感器等不同领域的技术融合。

此外,3D堆叠技术还可以减少晶片之间的数据传输距离,从而显著降低延迟,这对于需要实时处理大量数据的AI应用至关重要。未来3D堆叠技术有望成为半导体技术的主流,推动整个产业向更高效能、更低功耗的方向来发展。

■MOSAIC 3D AI晶片-全球首创运算与储存弹性延伸方案

随着AI处理器性能的提升,对于提供高算力和大频宽的高速记忆体需求也愈来愈迫切。目前关键记忆体存取技术就是高频宽记忆体(HBM),但因制作工序复杂且价格高贵,仅限用于高阶伺服器产品。

HBM记忆体虽是目前AI应用的首选,但许多科技业者也正积极寻求替代方案。工研院与力积电合作研发全球首款采用晶圆级记忆体+逻辑堆叠方案,设计出可弹性延伸的3D堆叠技术「MOSAIC 3D AI晶片」(Memory-cube Operability in a Stacked AI Chip;MOSAIC),使晶片间的传输距离从微米(um)大幅缩短至奈米(nm),大幅缩短记忆体与运算核心间的传输距离,显著提升资料传输频宽,产生的热能也仅十分之一,而最大优势在于灵活性与可扩展性,它使得不同应用场景下的晶片设计更加灵活,并能够快速响应市场需求变化,尤其共同打造的全球领先3D晶片堆叠一站式服务,成本也仅传统制程的五分之一。

MOSAIC技术的应用范围十分广泛,从高效能运算到AI加速器,甚至在物联网设备中也能发挥作用。此外,由于这种技术能够显著降低生产成本,工研院推出全球首款专为生成式AI应用所设计的MOSAIC 3D AI晶片,不仅拿下2024 R&D100大奖,更剑指市场一片难求的HBM,提供AI产业更高效能、高弹性、高性价比的替代方案,预计将会广泛推动AI和边缘运算的应用,从而彻底改变现有的半导体制造方式,视为一大革命性创新。

■AI晶片驱动半导体新世代

生成式AI技术兴起,各行各业对于高效能计算的需求倍增,促使晶片设计公司不断创新以应对新的挑战。AI晶片的趋势主要体现在:

一、定制化设计:随着不同AI应用场景的多样化,市场对于定制化AI晶片的需求增加。例如,针对自动驾驶、智能制造等领域的AI晶片要求具有高效能与低功耗的特性,而在智慧医疗和语音识别等领域,则需要更强大的数据处理能力与更高的精度。

二、异质整合:AI晶片不再仅限于传统的CPU与GPU架构,越来越多的设计公司开始探索异质整合,将CPU、GPU、NPU(神经处理单元)等不同的计算单元整合在一个晶片内,实现更高的计算效能与更低的能耗。这样的设计将使AI运算更加灵活,满足多样化的应用需求。

三、边缘运算的需求增长:随着5G与物联网技术的发展,边缘AI晶片的需求逐渐增加。这些晶片被设计用来在设备本地进行AI运算,降低了数据传输的延迟,同时也提高了隐私保护的水平。在未来,AI晶片不仅仅会应用于大型数据中心,还将广泛应用于智能家居、医疗设备、自动驾驶等领域。